超高压碳化硅 N 沟道 IGBT 器件的设计与制造

时间: 2022-06-17浏览次数:485

超高压碳化硅 N 沟道 IGBT 器件的设计与制造

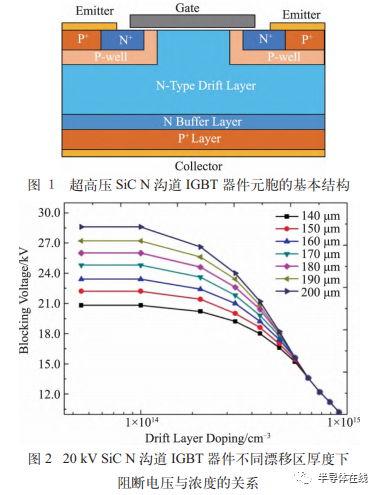

碳化硅(SiC)材料作为第三代半导体材料的代表之一,其禁带宽度达到 3.26 eV,是硅(Si)材料的 3 倍,临界击穿电场强度是 Si 材料的 10 倍,热导率接近 Si材料的 3 倍,被认为是下一代超高压功率器件的理想材 料。SiC 金 属 氧 化 物 半 导 体 场 效 应 晶体管(Metal-Oxide-Semiconductor Field-Effect Transistor,MOSFET)是目前最成熟、应用最广的 SiC 功率开关器件,然而随着功率器件的阻断电压不断增大,其导通电阻也会迅速增大,使其很难在超高压领域发挥重要作用。绝缘栅双极晶体管(Insulated Gate BipolarTransistor,IGBT) 作为现如今功率半导体器件的主要代表之一,综合了功率 MOSFET 和双极型晶体管(Bipolar Junction Transistor,BJT)两种器件的结构,正常导通状态下,会在其漂移层中发生电导调制效应,从而很好地降低了其漂移层的导通电阻以及整个器件的导通压降,极大地克服了高压 MOSFET 器件的缺点。早在 2007 年,美国 Cree 公司就报道了阻断电压为 9 kV 的平面栅 P 沟道 4H-SiC IGBT 器件,该器件的微分比导通电阻值为 88 mΩ·cm2,当时之所以采用 P 沟道,是因为 P 型 SiC 衬底电阻过大,无法支撑其制备 N 沟道 IGBT 器件。2009 年美国普渡大学利用数 值 模 拟 软 件 评 估 了 10 kV SiC MOSFET 和 SiCIGBT 器件的性能,指出 SiC IGBT 器件更适合应用于高压低频领域。Cree 公司在 2009 年采用厚度为100 μm、掺杂浓度为 3×1014 cm-3 的 N 型外延成功制备了耐压超过 13 kV 的 N 沟道 IGBT 器件,其微分比导通电阻值仅为 22 mΩ·cm2,远远低于 P 沟道 IGBT 器件。2015 年 Cree 公司和美国陆军实验室(Army Research Laboratory)共同合作,通过对比阻断电压为15 kV 的 4H-SiC MOSFET 和 N 沟道 4H-SiC IGBT 器件,发现 15 kV 4H-SiC MOSFET 器件的比导通电阻高达 204 mΩ·cm2,而同等级下的 N 沟道 4H-SiC IGBT器件仅为 50 mΩ·cm2,同时报道还指出通过在 N 沟道4H-SiC IGBT 器件结构中加入载流子存储层(Carrier Storage Layer,CSL),可以减小器件 JFET 区域的导通电阻,从而降低正向压降。2014 年 Cree 公司还联合了北卡罗来纳州立大学等高校,在 160 μm 的外延层上成功研制了 20 kV SiC N 沟道 IGBT 器件,在导通电流为 20 A 的条件下,其导通压降为 6.4 V。2016 年日立(Hitachi)的研发团队报道了具有极低开关损耗的 N 沟道 4H-SiC IGBT 器件,其漂移层厚度为 60 μm,阻断电压能够达到 6.5 kV,其开关损耗只有 1.2 mJ。在近几年研究发展过程中,Cree 公司甚至报道了阻断电压为 27 kV 的 N 沟道 SiC IGBT 器件,加入三代半交流群,加VX:tuoke08,器件的微分比导通电阻值仅为 123 mΩ·cm2。由于受 4H-SiC 单晶质量、外延生长技术的制约,国内对于 SiC IGBT 器件方面的实验研究起步相对较晚。南京电子器件研究所 SiC 团队于 2018 年成功研制出了 13 kV SiC N 沟道 IGBT 器件,但其导通特性较差。近年来通过对器件结构优化以及关键工艺技术的提升,SiC N 沟道 IGBT 器件取得了重大突破,缩短了与国外的差距。本文介绍了团队 SiC N 沟道 IGBT器件研制的最新成果。超高压 SiC N 沟道 IGBT 器件元胞的基本结构如图 1 所示。N+ 区域定义为源区,相应的电极称为发射极(Emitter)。背面 P+ 区域定义为漏区,相应的电极称为集电极(Collector)。超高压 SiC N 沟道 IGBT 器件与MOSFET 器件一样都是栅控型器件,栅区是器件的控制区域,相应的电极称为栅极(Gate)。器件沟道的形成在紧靠栅区边界处,其长度则由 P-well 区和 N+ 源区的横向扩散进行定义。场截止层(F-S)为高掺杂浓度的N+ 缓冲层,其主要作用在于使正向阻断状态下电场在该层降为 0,从而避免电场对 P+ 衬底的影响。IGBT 器件正面结构与功率 MOSFET 器件正面结构一致,唯一的不同之处在于器件的背面结构。IGBT 器件的背面结构是通过 P+ 外延层实现的,使得 IGBT 器件的背面结构比功率 MOSFET 器件多一个 PN 结,在导通状态下背面注入的少数载流子和正面的沟道载流子在 N漂移区复合,产生电导调制效应,大大降低了N漂移区的导通电阻。由于 SiC IGBT 器件的理论击穿电压主要由漂移区的厚度和掺杂浓度决定。为了使器件阻断电压超过20 kV,研究团队通过有限元仿真对漂移区的厚度和掺杂浓度进行优化设计,仿真结果如图 2 所示。观察得出当器件掺杂浓度较高时其阻断电压与外延层厚度无关,而当掺杂浓度较低时阻断电压基本正比于外延厚度。这主要是因为外延层掺杂浓度较高时,空间电荷区主要集中在外延层内部,此时外延层内电场为三角形分布且并未达到外延层底部,即使外延厚度发生变化电场的积分也无变化;而当掺杂浓度较低时,此时电场可近似为矩形,积分近似正比于外延厚度。但不能为了提高阻断电压一味提高外延厚度,因为过厚的外延层会导致正向导通电阻的增加,所以在保证阻断电压的同时要尽量使用较小的外延厚度。考虑到器件终端保护的效率问题和实际的器件应用需求,研究团队在设计材料参数时,将材料击穿电压需求设定为25 kV,预留 20%的设计冗余,在此条件下最终选取厚度为 180μm,掺杂浓度为 2×1014 cm-3的 N 型外延材料。

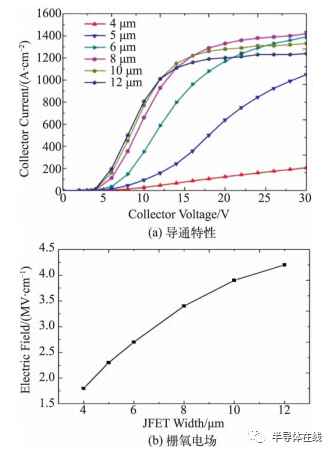

理论上,N 沟道 IGBT 器件的导通电阻主要由沟道电阻、漂移区电阻、JFET 区电阻以及一系列接触电阻组成。对于击穿电压超过 20 kV 的 SiC IGBT 器件而言,对其导通电阻影响最大的是垂直 JFET 区电阻,而垂直 JFET 区设计优化主要是对 JFET 区的宽度和掺杂浓度进行优化。加大 JFET 区的横向长度和掺杂浓度可以显著减小器件导通电阻,但在阻断状态时,延伸的耗尽区不容易夹断,对栅氧化层底部电场强度的抑制作用减弱,可能会引起器件提前击穿。缩小 JFET区的横向长度和掺杂浓度会增强对栅氧化层底部电场的抑制作用,器件在高电压下的稳态性变好,但同时会引起器件导通电阻的增加,导致稳态电流的下降,因此需要统筹考虑 JFET 区对于器件导通特性和击穿电压之间的关系,不同 JFET 宽度下器件的导通特性以及截取的栅极氧化层电场如图 3 所示。观察发现随着 JFET 区宽度从 4 μm 扩展至 12 μm 时,增大垂直 JFET 区的宽度可以降低沟道导通电阻,使导通电流增大。但随着 JFET 区进一步增大,元胞尺寸的增大效应也将变得明显,使得器件导通电流密度随 JFET宽度增加而增长的速率减缓,同时反向偏置状态下P-well 区的夹断作用降低,栅氧化层底部电场提高。理论上,氧化层击穿是指氧化层电场在反向阻断时超过自身临界场强的情况,一般认为 SiO2 的电场不应超过3 MV/cm。因此在保证器件可靠性的同时,为实现尽可能高的器件导通能力,元胞结构最终采用 6 μm 的JFET 区域。

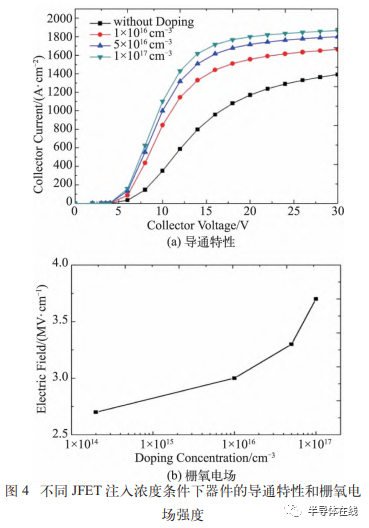

由于 SiC IGBT 器件超高的耐压要求,器件漂移区一般保持非常低的掺杂浓度,这往往会导致垂直JFET 区电阻大大增加,因此在 20 kV SiC IGBT 器件研制中,通过引入 JFET 区注入掺杂技术,可更有效地提升器件导通特性,仿真结果如图 4(a)所示。观察发现随着 JFET 区掺杂浓度的增大,器件导通电流随之增大,主要是因为 JFET 区掺杂浓度增大,器件导通时P-well 区两侧的耗尽区宽度大幅度减小,JFET 区电阻减小,器件导通电阻也随之减小。与此同时该器件反向偏置状态下 P-well 区的夹断作用降低,栅氧化层底部电场提高,不同 JFET 浓度下栅氧化层电场如图 4(b)所示。综合考虑器件的导通压降和阻断电压,元胞结构采用浓度为 1×1016 cm-3 的 JFET 区注入条件。

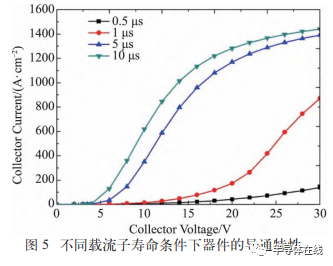

高载流子寿命是实现大功率 SiC 双极型器件的关键技术之一。不同载流子寿命下器件的导通特性如图5 所示。观察发现随着载流子寿命的增加,器件的导通电流增加,主要是因为少数载流子寿命的增强可以显著改善双极型器件的电导调制效应,有利于实现较低的器件导通压降。仿真结果显示,为了达到较好的导通特性,器件的载流子寿命最好能够达到5 μs 以上。

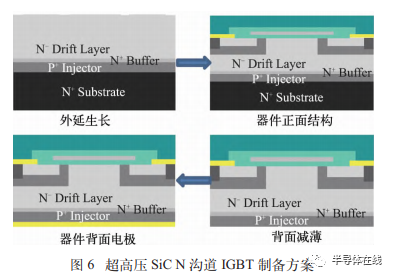

研究团队设计的 SiC IGBT 器件为 N 沟道 SiC IGBT 器件,N 型 SiC 衬底电阻率约为 0.025 Ω·cm,而P 型 SiC 衬底电阻率约为2.5 Ω·cm,因此如果在350 μm P 型 SiC 衬底上制造 N 沟道 SiC IGBT 器件,此时 P 型衬底电阻值甚至大于所设计器件的导通电阻值,再加上目前国内很难供应 P 型 SiC 衬底,因此团队提出一种在 N 型 SiC 衬底上进行器件设计与制造的方案。具体的制备方案如图 6 所示。通过在 N 型4H-SiC 衬底上生长所需的关键外延层,包括 N漂移层,N+缓冲层以及 P+ 集电极层;采用 SiO2 作为各区域的注入掩模,由多次 P 型离子注入实现 P-well 区和 P+区域,多次高剂量 N 型离子注入实现 N+ 区域。同时为了有效降低该器件 JFET 区的电阻,单独对 JFET 区域进行 N 型离子注入,所有注入完成后在 1650 ℃的氩气(Ar)环境下退火以激活注入离子。退火后,通过牺牲氧化去除表面碳层,湿法表面清洗后放入高温氧化炉中进行干氧氧化,形成栅氧化层。采用一氧化氮(NO)高温退火技术,有效降低栅氧界面陷阱密度,最终氧化层厚度控制在 50 nm 左右。在栅氧工艺完成后,通过在栅氧化层上沉积多晶硅实现栅电极的制作。采用氧化硅 / 氮化硅(SiO2/SiN)介质实现栅极和发射极隔离以及表面钝化。发射极的欧姆接触由金属镍(Ni)实现,介质孔刻蚀后通过加厚铝(Al)层完成发射极单胞之间的互联。器件正面结构完成后通过减薄 / 背面研磨的方法去除 N 型衬底,保留部分 P+ 层,接着蒸发背面欧姆金属,考虑到普通的背面欧姆制作工艺需要相当高的温度,过程中的高温会损伤表面器件结构,因此采用激光退火工艺完成背面的欧姆制作。

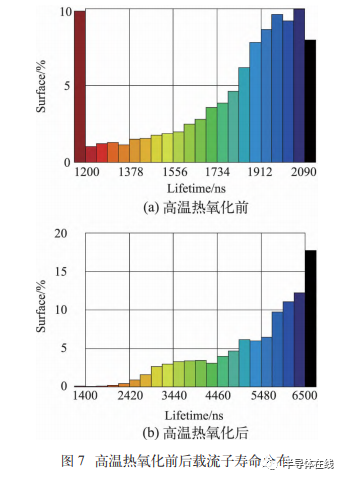

由于 IGBT 器件电导调制效应的存在,使得载流子寿命高低成为影响漂移区电阻高低的重要因素之一。在 N 型 SiC 材料的早期研究阶段,Z1/2 缺陷中心被公认为是载流子寿命的“杀手”。到目前为止,国际上主要采用两种相对成熟的技术来消除 Z1/2 缺陷中心:1)从外部引入过量的碳原子,并且通过高温退火来促进碳原子体区扩散;2)在适当条件下,通过长时间高温热氧化消除 Z1/2 缺陷中心。考虑到碳注入结合高温退火的方法在高能碳离子注入过程中容易引入新的缺陷,同时受碳注入深度的限制,对厚层 SiC 外延来说效果不够理想,因此本研究采用长时间高温热氧化工艺来提升载流子寿命。研究团队首先采用 μ-PCD 测量方法测量 SiCIGBT 厚外延片材料的少子寿命,高温热氧化前分布如图 7(a)所示,其少子寿命平均值大约在 1.76 μs,后续将该外延片经过 10 h 的高温热氧化,去除表面氧化层清洗处理后,再次测量其少子寿命,结果如图 7(b)所示,其平均值提升至 5.42 μs。从实验结果看,长时间的高温氧化工艺对于器件的少子寿命有较大的提升作用,主要原因在于高温热氧化的过程中,部分碳原子会扩散到体区并填补碳空位,消除 Z1/2 缺陷中心。

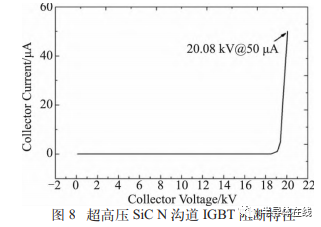

制备的 20 kV SiC IGBT 器件芯片单胞长度为14 μm,沟道长度为 1.0 μm,器件采用了总宽度为1.4 mm 的场限环终端,总尺寸达到 9.2 mm×9.2 mm,其中有源区面积为 30 mm2。对超高压 SiC N 沟道 IGBT 器件的正向阻断特性进行测试,必须将器件的栅极与发射极接地,在集电极加正电压。而且考虑到设计的器件阻断电压大于18 kV,因此在测试过程中,需要将芯片浸泡在高压测试油中,从而隔绝空气。室温下正向阻断特性测试结果如图 8 所示,该器件在室温下击穿电压可以达到20 kV。当集电极电压为 20.08 kV 时,漏电流为 50 μA,为目前国内研制的最高击穿电压 SiC IGBT 器件。

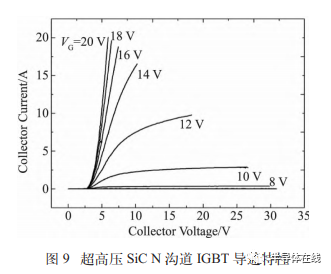

SiC N 沟道 IGBT 器件的正向导通特性测试一般在发射极接地、栅极加正偏压的情况下进行。不同栅压下的集电极电流随着集电极电压的变化曲线如图 9所示。室温下,该器件在栅压为 20 V,集电极电流为20 A 时,集电极导通电压为 6.0 V,此时其微分比导通电阻为 27 mΩ·cm2,该值与国际上相同击穿电压器件的微分比导通电阻最低值相当。

为了更好地反映载流子寿命对于器件导通特性的影响,本文分析了芯片 A(引入载流子寿命提升工艺)、芯片 B(未引入载流子寿命提升工艺)的实验结果以及仿真结果,具体高温热氧化处理前后超高压 SiC N 沟道 IGBT 导通特性如图 10 所示。观察发现芯片 B在栅极电压为 20 V、集电极电流密度为 70 A/cm2 的条件下,器件导通压降为 16.2 V 左右,引入载流子寿命提升工艺后,芯片 B 在同等测试条件下,其导通压降降至 6.5 V 左右,这一结果也恰好验证了载流子寿命的提升能有效提高 SiC N 沟道 IGBT 器件的导通能力。

声明:本文版权归原作者所有,转发仅为更大范围传播,若有异议请联系我们修改或删除:zhangkai@cgbtek.com